Exam Details

Exam Code

:EN0-001Exam Name

:ARM Accredited EngineerCertification

:ARM CertificationsVendor

:ARMTotal Questions

:210 Q&AsLast Updated

:Jun 28, 2025

ARM ARM Certifications EN0-001 Questions & Answers

-

Question 71:

The Cortex-A9 MPCore processor contains a hardware block whose function is to maintain data cache coherency between cores. What is the name of this block?

A. Shareable Memory

B. Snoop Control Unit

C. Private Memory Region

D. Level 2 Cache Controller

-

Question 72:

Which TWO of the following accurately describe constraints on the location of the Tightly Coupled Memory (TCM) regions in a Cortex-R4 processor? (Choose two)

A. TCM Region A (ATCM) must be at a lower memory address than TCM Region B (BTCM)

B. TCM Region A can only be located at address 0x0

C. Both TCM regions must be placed at addresses which are aligned to their size

D. The two TCM regions may not overlap

E. TCM Region B (BTCM) must be located immediately above TCM Region A (ATCM)

-

Question 73:

Which of the following processor resources do NOT have to be saved or modified by the Linux scheduler during context switch?

A. Registers R0-R15

B. Thread and process ID registers

C. The CPSR

D. NEON and VFP registers

-

Question 74:

A function written in C has the prototype:

void my_function(float a. double b, float c);

The function is built and linked into an application using hard floating-point linkage. What registers are

used to pass arguments to the function?

A. a->s0; b->d0; c->s1

B. a->s0; b->d1; c->s1

C. a->d0; b->d1; c->d2

D. a->s0; b->d1; c-> s2

-

Question 75:

Under which of the following circumstances is TLB maintenance always required?

A. If a TLB miss occurs

B. On every process switch

C. If the TLB reports a fault

D. When a page table entry is changed

-

Question 76:

Which one of the following debug methods is the least intrusive for analyzing a timing related bug?

A. Place breakpoints on strategic locations to locate the problem area

B. Instrument the code with print statements to locate the problem area

C. Use debug hardware to place watchpoints on strategic data memory locations

D. Use trace hardware to capture a trace log up to the point of the crash

-

Question 77:

In a Cortex-A processor, after which TWO of these events is a cache maintenance operation required to ensure reliable code execution? (Choose two)

A. Processor reset

B. Switching from ARM to Thumb state

C. Changing the access permissions of a page

D. Executing a Data Memory Barrier instruction

E. Loading data from an unaligned memory address

-

Question 78:

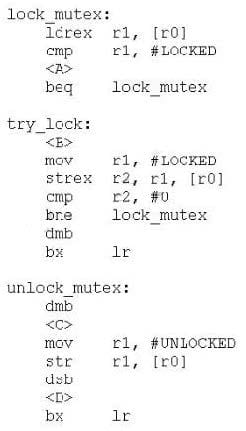

The following pair of functions implement a simple mutex spinlock which might be used to protect a critical code section in a multi-threaded application. The address of the lock variable is in r0.

In order to minimize power while waiting for the lock to be available. SEV and WFE instructions can be used to place the processor in a low power state while waiting for the lock to become available. At which points should these instructions be placed?

A. WFENE at , SEV at

B. WFEEQ at SEV at

C. WFE at SEV at

WFENE at D. SEV at

-

Question 79:

Cortex-A series processors contain event counting hardware which can be used to profile and benchmark code. The counters for these are programmed using:

A. Memory-mapped registers.

B. Generic Interrupt Controller (GIC) registers.

C. Debug Coprocessor Registers (CPU).

D. System Control Coprocessor Registers (CP15).

-

Question 80:

When using an Operating System, which instruction is used by user code to request a service from the kernel?

A. BLX

B. RFEFD

C. SRSFD

D. SVC

Related Exams:

Tips on How to Prepare for the Exams

Nowadays, the certification exams become more and more important and required by more and more enterprises when applying for a job. But how to prepare for the exam effectively? How to prepare for the exam in a short time with less efforts? How to get a ideal result and how to find the most reliable resources? Here on Vcedump.com, you will find all the answers. Vcedump.com provide not only ARM exam questions, answers and explanations but also complete assistance on your exam preparation and certification application. If you are confused on your EN0-001 exam preparations and ARM certification application, do not hesitate to visit our Vcedump.com to find your solutions here.