Exam Details

Exam Code

:EN0-001Exam Name

:ARM Accredited EngineerCertification

:ARM CertificationsVendor

:ARMTotal Questions

:210 Q&AsLast Updated

:Jun 28, 2025

ARM ARM Certifications EN0-001 Questions & Answers

-

Question 121:

A re-entrant interrupt handler would typically be used to:

A. Allow an external interrupt to interrupt an SVC handler

B. Reduce response time for higher priority interrupts

C. Allow an interrupt handler to be relocated in memory

D. Avoid the need for an interrupt handler to use a stack.

-

Question 122:

Capturing processor execution trace is characterized as being:

A. Influenced by breakpoints.

B. Intrusive on normal processor operation.

C. Inaccurate regarding code execution history.

D. Not intrusive on normal processor operation.

-

Question 123:

Why does Device memory prohibit speculative accesses?

A. Speculative accesses might waste energy

B. Speculative accesses might reduce performance

C. Speculative accesses might cause unwanted cache coherency traffic

D. Speculative accesses might cause undesired system state changes

-

Question 124:

What is the value of R2 after execution of the following instruction sequence? MOV R3, #0xBA

MOV R2/#0x10 BIC R2, R3, R2

A. R2 = 0xBB

B. R2 = 0xCB

C. R2 = 0xAA

D. R2 = 0xCC

-

Question 125:

The interval of time from an external interrupt request signal being raised to the first fetch of an instruction of the interrupt handler is called the interrupt:

A. Latency

B. Priority

C. Service thread

D. Jitter

-

Question 126:

The Memory Protection Unit (MPU) of Cortex-R4 performs which of the following tasks?

A. Translates virtual addresses to physical addresses

B. Generates parity information to detect soft errors in memory

C. Performs access permission checks

D. Permits the system to be divided into secure and normal worlds, through the use of ARM's TrustZone technology

-

Question 127:

How many ARM core registers and PSRs (Program Status Registers) are available to the programmer in User mode on a Cortex-A9?

A. 16

B. 17

C. 18

D. 32

-

Question 128:

Implementing loops using a decrementing counter which exits the loop when a counter reaches zero can be beneficial for power and performance. This is because:

A. A simpler branch instruction can be used.

B. Decrementing variables uses less power than incrementing them.

C. The decrement and branch operations can be encoded as a single instruction.

D. The loop termination condition check can be integrated into the subtract operation.

-

Question 129:

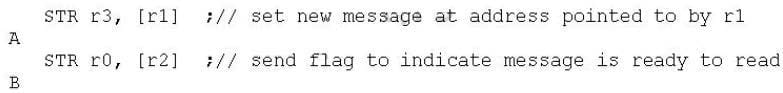

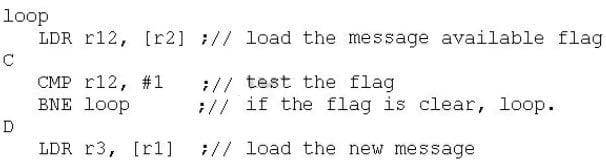

A message passing system between two CPUs is implemented using data stored in a shared area of

memory. To pass a message, the first CPU executes the instructions:

The second CPU receives the message using the instructions:

On both CPUs, r1 = 0x5000 and r2 = 0x6000. At which of the points A, B, C and D must Data Memory Barrier (DMB) instructions be placed in order to ensure messages are passed reliably and efficiently?

A. A only

B. C only

C. B and C

D. A and D

-

Question 130:

In the CPSR, 1=0 and F=1. Which of the following is TRUE in this case?

A. Both IRQs and FIQs are enabled

B. Both IRQs and FIQs are disabled

C. IRQs are disabled and FIQs are enabled

D. IRQs are enabled and FIQs are disabled

Related Exams:

Tips on How to Prepare for the Exams

Nowadays, the certification exams become more and more important and required by more and more enterprises when applying for a job. But how to prepare for the exam effectively? How to prepare for the exam in a short time with less efforts? How to get a ideal result and how to find the most reliable resources? Here on Vcedump.com, you will find all the answers. Vcedump.com provide not only ARM exam questions, answers and explanations but also complete assistance on your exam preparation and certification application. If you are confused on your EN0-001 exam preparations and ARM certification application, do not hesitate to visit our Vcedump.com to find your solutions here.